# Working with PLLs in PrimeTime – avoiding the "phase locked *oops*"

## Paul Zimmer

Zimmer Design Services 1375 Sun Tree Drive Roseville, CA 95661

paulzimmer@zimmerdesignservices.com

website: www.zimmerdesignservices.com

#### **ABSTRACT**

.

PLLs play an important role in modern high-speed designs, especially when configured for clock tree insertion delay cancellation (IDC). Modeling the behavior of such PLLs accurately in PrimeTime can be a challenge. This paper discusses basic modeling techniques for both standard and multiplier IDC PLLs, duty cycle modeling, jitter and skew, and on-chip-variation effects. The classic OCV/PLL excess pessimism problem will be explained and examined, and a couple of workarounds will be discussed, including a novel new technique developed by the author.

## **Table of contents**

| 1  | Introduction                                                   |                             |

|----|----------------------------------------------------------------|-----------------------------|

| 2  | The basic insertion delay cancellation (idc) PLL               | 4                           |

| 2  | .1 The problem – too much delay                                | 4                           |

| 2  | .2 The solution – the insertion delay cancellation PLL         | 5                           |

|    | .3 Timing the basic idc PLL in PrimeTime                       |                             |

|    | .4 The IDC multiplier PLL                                      |                             |

|    | .5 The PLL model itself                                        |                             |

| 2  | .6 Performance considerations                                  | <u>24<del>25</del></u>      |

| 3  | Duty Cycle                                                     |                             |

| 3  | .1 Internal clocks (other than PLLs)                           | <u>25</u> 26                |

| 3  | .2 Primary input clocks and PLLs                               | <u>27<del>28</del></u>      |

|    | .3 Applying this to our multiplier pll circuit                 |                             |

| 3  | .4 When to use these techniques                                | <u>4041</u> 39              |

| 4  | Jitter                                                         | <u>4142</u> 40              |

| 4  | .1 Jitter, skew, and uncertainty                               | <u>4142</u> 40              |

| 4  | .2 My definition of jitter                                     | <u>4142</u> 40              |

|    | .3 Sources of jitter                                           |                             |

|    | .4 Effects of jitter on different sorts of paths               |                             |

|    | .5 Modeling jitter with set_clock_uncertainty                  |                             |

|    | .6 Applying jitter specs to the example circuit – simple case  |                             |

|    | .7 Generated clocks                                            |                             |

|    | .8 What about falling edges?                                   |                             |

|    | .9 Applying jitter specs to the example circuit – complex case |                             |

| 5  | On-chip Variation                                              |                             |

|    | .1 The classic OCV case                                        |                             |

|    | .2 Enter CRPR                                                  |                             |

|    | .3 OCV and PLLs                                                |                             |

| 5  | .4 The OCV/PLL excess pessimism problem                        |                             |

| 6  | OCV/PLL excess pessimism workarounds                           |                             |

|    | .1 Forcing OCV off on the fb path                              |                             |

|    | .2 Referencing the i/os to the feedback clock                  |                             |

|    | .3 The shell game                                              |                             |

| 7  | Conclusion                                                     | <u>110<del>111</del>109</u> |

| 8  | Acknowledgements                                               | <u>111<del>112</del>110</u> |

| 9  | References                                                     | <u>112<del>113</del>111</u> |

| 10 | Appendix                                                       | 113 <del>114112</del>       |

| -  | 0.1 The PLL model itself                                       |                             |

|    | 0.2 Why I do it my way                                         |                             |

|    | 0.3 Modeling duty cycle using set_clock_latency early/late     |                             |

|    | 0.4 Modeling duty cycle using set_clock_latency min/max        |                             |

## 1 Introduction

PLLs are an absolutely essential tool in high-speed design. Their ability to nearly zero out the delay of a large clock tree allows for much higher speed inter-chip communication.

However, modeling PLLs in static timing analysis is tricky. Many of the details have been glossed over or ignored in the past, but as circuit feature sizes decrease and speeds increase, it is no longer acceptable to depend on over-constrained budgets or just plain dumb luck to be sure the PLL will work in the intended application. Certain effects, such as on-chip variation and signal integrity analysis, make correct operation of the circuit absolutely dependent on a complete, accurate static timing analysis – and this includes the PLL.

## 2 The basic insertion delay cancellation (idc) PLL

PLLs are common in modern high-speed designs. The inner workings of the pll are more the domain of analog sorcerers, but the basic idea is this: "the pll makes its output do whatever is necessary to make its ref and fb inputs match in phase and frequency".

There are many uses for PLLs. The one I'll be discussing here is what I call the "insertion delay cancellation" pll.

## 2.1 The problem – too much delay

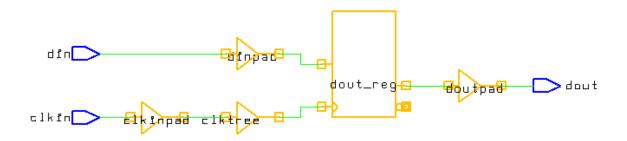

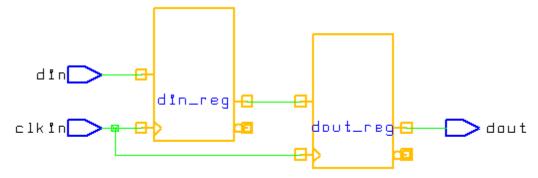

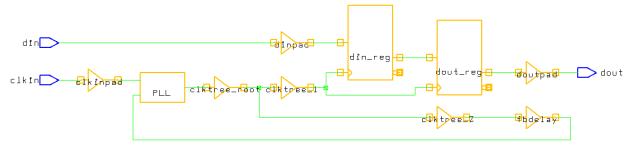

Here is a very basic i/o circuit. Data and clock are sent in and data comes out. The outgoing data is clocked externally by the same clock that is sent to the circuit.

Figure 2-1

And here's what the timing waveform looks like:

Figure 2-2

It is clear that all of the delays in generating the data (clock pad, clock tree insertion delay, etc)

will reduce the available setup time of dout and therefore limit the frequency of operation.

## 2.2 The solution – the insertion delay cancellation PLL

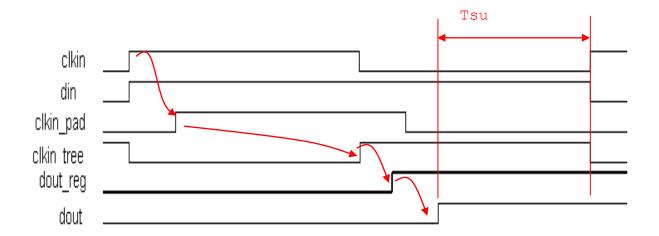

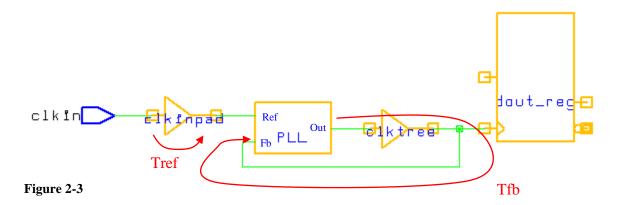

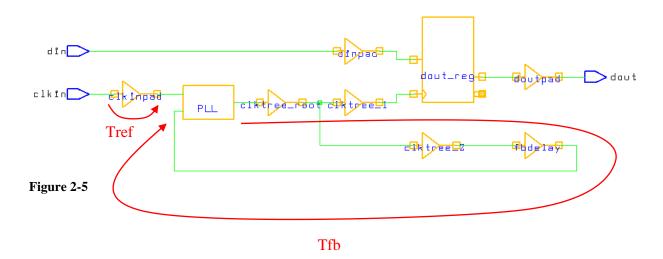

To get around this problem, designers often insert a PLL into the clock path. The configuration looks like this:

The Fb input of the pll is connected to the *end* of the clock tree.

Remember that the pll must drive its output such that its ref and fb inputs match in phase and frequency. The frequency part is easy – it just matches clkin's frequency, which reappears on the Fb pin. What about the phase?

Ignore Tref for now. If the clock at Ref arrived at time zero, the pll would have to drive its output *back in time* by Tfb to make the signal arrive at the Fb pin at time zero. So, it would launch the clock at time –Tfb. But, clkin appears at the pll Ref pin at time Tref. So, the pll doesn't have to drive its output back by the full Tfb, but only by Tfb – Tref. In other words, it launches its clock at time Tref – Tfb. After passing through the feedback loop, the clock arrives at the Fb input at time Tref, which is what we want.

The net effect of this is that the flops on the end of the clock tree get clocked at *almost* time zero. They get clocked at time Tref. If we add a little extra delay to the feedback path to match Tref, we can get the flops clocked at time zero relative to clkin. This allows us to "cancel" the insertion delay of the clock tree. So, a more realistic idc pll might look like this:

Figure 2-4

## 2.3 Timing the basic idc PLL in PrimeTime

So, how do we go about modeling this in Primetime? The most straightforward approach (although not the only approach, as we shall see later) is to model what happens in real life – create a clock on the pll output pin with a frequency to match clkin, and then "launch" this pll output clock at time Tref-Tfb. We then allow the two clocks to time against one another. The "launch" is accomplished with the set\_clock\_latency command, so the commands would look something like this:

```

create_clock -period 10.0 -name clkin [get_ports clkin]

set_propagated_clock clkin

create_clock -period 10.0 -name pllout [get_pins PLL/OUT]

set_propagated_clock pllout

set_clock_latency -source \

[expr $_ref_delay - $_fb_delay] \

[get_clocks pllout]

```

The problem is, how do we get the values of \$\\_ref\_delay and \$\\_fb\_delay?

Reference [4] gives one approach. I use a different approach. I use get\_timing\_paths to get the values. I think mine is simpler to code. It also takes advantage of the fact that, by creating all the clocks first, it is possible to extract the feedback delay as an arrival attribute on the fb pin. Also, reference [4] puts the values into files that are then sourced by multiple Primetime runs. I'm not that trusting, so I force PT to calculate the value every time the script runs.

## My approach is like this:

- 1. Create all the clocks, including the pll output clock (but don't set the source latency yet).

- 2. Get Tref and Tfb using get\_timing\_paths.

- 3. Calculate the source latency (Tref Tfb) and apply it to the pll output clock. The source latency value will usually be negative.

- 4. Use set\_input\_delay and set\_output\_delay with the reference clock to specify the i/o timing.

- 5. Allow the clocks to time against each other (don't do set false path between them)

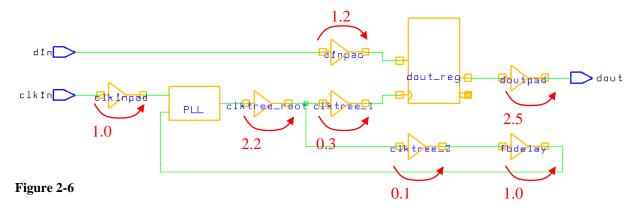

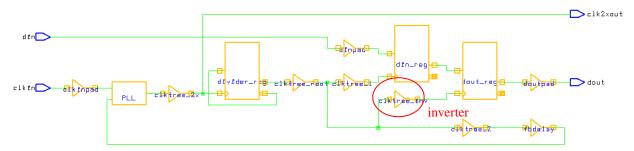

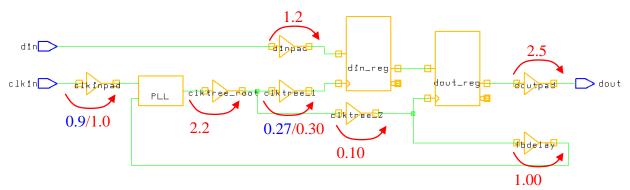

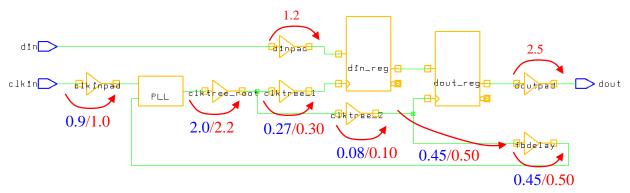

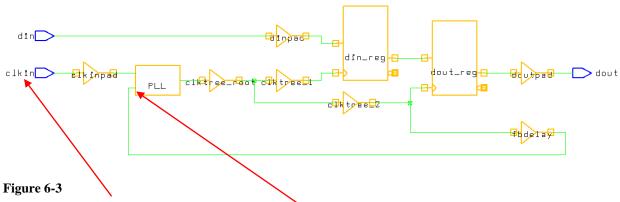

Here's an example circuit. I have added a flip-flop on the end of the clock tree. The flop clocks data in through the din pad, and sends data out through the dout pad. Notice also that this flop is on a slightly different branch of the clock tree than the one the pll feedback is hooked up to. They share clktree\_root, but not clktree1 (to the flop) or clktree2 (to the pll feedback).

First, we'll create the clocks. Doing this first makes it easier to get the delay values we want:

```

create_clock -period 10.0 -name clkin [get_ports clkin]

set_propagated_clock clkin

create_clock -period 10.0 -name pllout [get_pins PLL/OUT]

set_propagated_clock pllout

```

Because the clocks exists, we can get the timing values we want by just getting the "arrival" attribute on the path:

```

set _path [get_timing_paths -delay max_rise \

-from [get_ports clkin] \

-to [get_pins PLL/CKREF] \

]

set _ref_delay [get_attribute $_path arrival]

set _path [get_timing_paths -delay max_rise \

-from [get_pins PLL/OUT] \

-to [get_pins PLL/FB] \

]

set _fb_delay [get_attribute $_path arrival]

```

Note the use of "-delay max\_rise". We want a rise delay because the pll runs on rising edges (most do, anyway). Without on-chip-variation (OCV), the min\_rise and max\_rise values should be the same. OCV effects will be discussed later.

Also note that \_ref\_delay is set by getting the arrival attribute on the path returned by get\_timing\_paths, which is a collection. I expect this collection to have only one path in it. If I have done something wrong and the collection has more than one path, the "set \_ref\_delay" command will cause an error. I call this poor-man's error checking...

## When I run this script, I get:

```

pt_shell> echo $_ref_delay

1.000000

pt_shell> echo $_fb_delay

3.300000

pt shell>

```

Let's verify this using report\_timing. We'll need to set the variable timing report unconstrained paths to "true" to see a result.

```

pt shell> set timing report unconstrained paths true

true

pt shell> report timing -input pins -delay max rise -from [get ports clkin] -

to [get_pins PLL/CKREF]

Report : timing

-path full

-delay max rise

-input pins

-max paths 1

Design : idc pll example

Version: V-2\overline{0}04.\overline{0}6

*********

Startpoint: clkin (clock source 'clkin')

Endpoint: PLL/CKREF (internal pin)

Path Group: (none)

Path Type: max

Point

clock source latency

0.00

0.00

clkin (in)

0.00

0.00 r

clkinpad/I (bufbd1)

0.00

0.00 r

clkinpad/Z (bufbd1)

1.00 *

1.00 r

PLL/CKREF (DUMMYPLL)

0.00

1.00 r

data arrival time

1.00

______

(Path is unconstrained)

```

```

pt_shell> report_timing -input_pins -delay max_rise -from [get_pins PLL/OUT] -

to [get pins PLL/FB]

*********

Report : timing

-path full

-delay max rise

-input pins

-max paths 1

Design : idc pll example

Version: V-2\overline{0}04.\overline{0}6

*******

Startpoint: PLL/OUT (clock source 'pllout')

Endpoint: PLL/FB (internal pin)

Path Group: (none)

Path Type: max

Point

_____

clock source latency

0.00

0.00

PLL/OUT (DUMMYPLL)

0.00

0.00 r

clktree_root/I (bufbd1)

0.00

0.00 r

clktree_root/Z (bufbd1)

2.20 * 2.20 r

clktree_2/I (bufbd1)

0.00

2.20 r

clktree_2/Z (bufbd1)

0.10 * 2.30 r

fbdelay/I (bufbd1)

0.00

2.30 r

fbdelay/Z (bufbd1)

1.00 * 3.30 r

PLL/FB (DUMMYPLL)

0.00

3.30 r

data arrival time

3.30

data arrival time

3.30

_____

(Path is unconstrained)

```

Looks correct. \$\\_ref\_\delay is 1.0 and \$\\_fb\_\delay is 3.3.

Now we'll apply this source latency:

```

set_clock_latency -source \

[expr $_ref_delay - $_fb_delay] \

[get clocks pllout]

```

When we do this, we'll get the following warning:

```

Warning: Negative clock latency specified: -2.3 (UITE-150)

```

This is harmless. We normally expect a negative source delay on the pll output clock (because the fb path is usually longer than the refclk path).

To make sure we got what we wanted, do report\_clock –skew:

Just to make absolutely sure this all worked, here's some code that verifies that the arrival time at the CKREF pin matches the arrival time at the FB pin within some small rounding error:

```

# Verify

# Get the new fb path delay

set path [get_timing_paths -delay max rise \

-to [get pins PLL/FB] \

set new fb delay [get attribute $ path arrival]

# Get the ref clock delay

set path [get timing paths -delay max rise \

-from [get_ports clkin] \

-to [get pins PLL/CKREF] \

set new ref delay [get attribute $ path arrival]

set diff [expr $ new ref delay - $ new fb delay]

if { ($ diff > 0.01) || ($ diff < -0.01)</pre>

echo "Error: Difference between FB and REF pins out of range!"

echo " Difference is $ diff"

echo " _ref_delay is $_ref_delay"

echo " _fb_delay is $_fb_delay"

} else {

echo "PLL timing verified!"

```

#### When we run this, we get:

PLL timing verified!

Now we need to constrain the data paths. The din/dout paths are part of an interface that is referenced to clkin, so we'll set the input and output delays accordingly.

```

set_input_delay -max 8.0 -clock clkin [get_ports din]

set_input_delay -min 0.5 -clock clkin [get_ports din]

set_output_delay -max 2.0 -clock clkin [get_ports dout]

set_output_delay -min [expr -1.0 * 0.5] -clock clkin [get_ports dout]

```

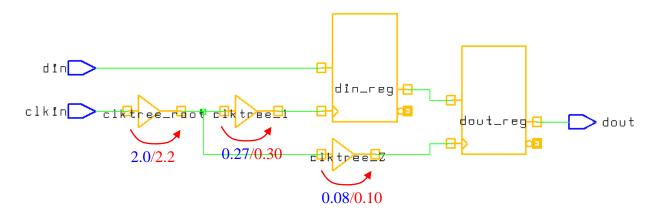

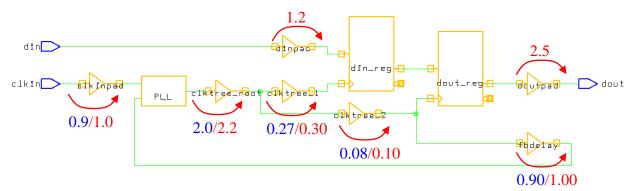

Now let's look at the timing. Here's the schematic again, with the delays of each buffer shown:

A couple of things to notice about this. I have made the fbdelay match the clkinpad delay exactly, but the clktree\_1 and clktree\_2 buffers don't match exactly. The clock tree has 0.2ns of *real* skew.

## First we'll look at the din timing:

```

pt shell> report timing -input pins -path type full clock expanded -from din

*********

Report : timing

-path full_clock_expanded

-delay max

-input pins

-max paths 1

Design : idc pll example

Version: V-2\overline{0}04.\overline{0}6

*********

Startpoint: din (input port clocked by clkin)

Endpoint: dout reg (rising edge-triggered flip-flop clocked by pllout)

Path Group: pllout

Path Type: max

Path

Incr

______

clock clkin (rise edge)

0.00

0.00

clock network delay (propagated)

0.00

0.00

input external delay

8.00

8.00 r

din (in)

0.00

8.00 r

dinpad/I (bufbd1)

0.00

8.00 r

1.20 * 9.20 r

0.00 9.20 r

dinpad/Z (bufbd1)

dout reg/D (dfnrb1)

9.20

data arrival time

clock pllout (rise edge)

clock source latency

PLL/OUT (DUMMYPLL)

clktree_root/I (bufbd1)

clktree_root/Z (bufbd1)

clktree_1/I (bufbd1)

clktree_1/Z (bufbd1)

dout_reg/CP (dfnrb1)

dout_reg, or ...

library setup time

data required time

data required time

data arrival time

______

slack (MET)

0.92

```

If the insertion delay cancellation were perfect, we would expect the clock to arrive at dout\_reg/CP at time 10.0 (one full period of the clock). Instead, it arrives at 10.2. Why? Because the clock tree had skew. The clktree\_2 buffer was 0.2ns faster than the clktree\_1 buffer. This means the feeback delay from the pll was slightly less than it should have been, resulting in a late arriving clock.

#### Now let's look at the dout timing:

```

pt shell> report timing -input pins -path type full clock expanded -to dout

*********

Report : timing

-path full_clock_expanded

-delay max

-input pins

-max paths 1

Design : idc pll example

Version: V-2\overline{0}04.\overline{0}6

*********

Startpoint: dout reg (rising edge-triggered flip-flop clocked by pllout)

Endpoint: dout (output port clocked by clkin)

Path Group: clkin

Path Type: max

Incr

______

0.00 0.00

-2.30 -2.30

0.00 -2.30 r

0.00 -2.30 r

2.20 * -0.10 r

0.00 -0.10 r

clock pllout (rise edge)

clock source latency

PLL/OUT (DUMMYPLL)

clktree_root/I (bufbd1)

clktree_root/Z (bufbd1)

clktree_1/I (bufbd1)

clktree_1/I (bufbd1)

clktree_1/Z (bufbd1)

dout_reg/CP (dfnrb1)

dout_reg/Q (dfnrb1)

doutpad/I (bufbd1)

doutpad/Z (bufbd1)

doutpad/Z (bufbd1)

dout (out)

data arrival time

clock clkin (rise edge)10.0010.00clock network delay (propagated)0.0010.00output external delay-2.008.00

8.00

data required time

______

data required time

data arrival time

-3.02

_____

```

In this case, we're launching data from the pll domain and capturing it in the clkin domain. So, the capture clock is at 10.0. But the launch clock at dout\_reg/CP is 0.20 – once again it is 0.2ns late (for the same reason explained above).

Both of these path reports are correct – we have modeled the pll behavior correctly.

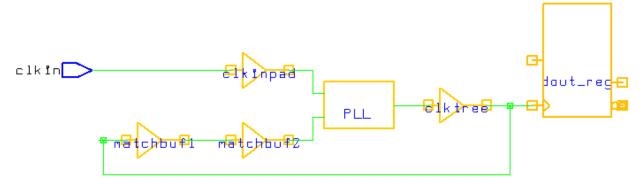

## 2.4 The IDC multiplier PLL

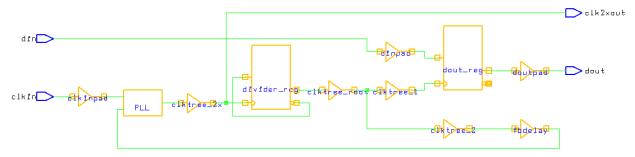

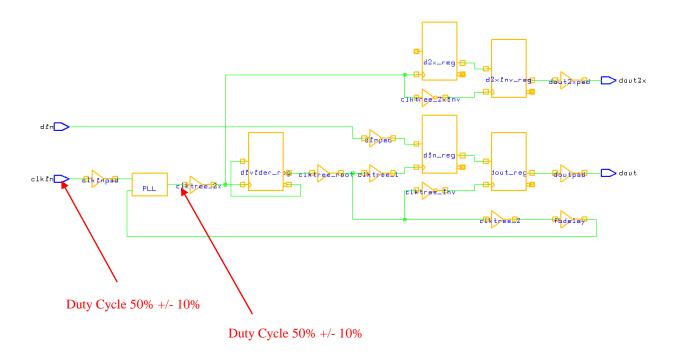

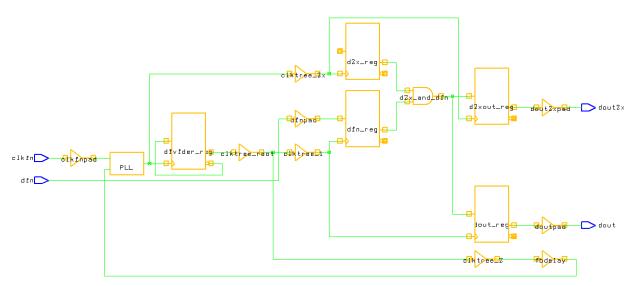

Now lets try a slightly more complicated example. Consider this circuit:

Figure 2-7

Remember that the pll must drive its output such that its ref and fb inputs match in phase and frequency. Since there is a divide-by 2 in the fb path, the pll will have to drive its output at twice the frequency of clkin to make the frequency match at the fb pin. This is a frequency multiplier pll.

There are several reasons why you might want to do this. You might need the 2x clock internally for other functions, for example. In that case, the i/os would be connected to the divide-by output. Or you might be doing something really wierd, like running the data at 2x speeds anchored by the 1x reference clock.

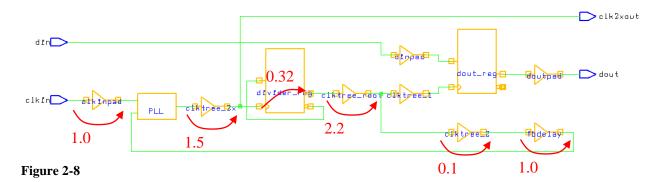

How do we model this in PrimeTime? Well, it turns out that the procedure outlined above still works. Here's the circuit again with all the delays shown:

The first step was, "create all the clocks". The first two clocks are the same as before, except that the period of the pll clock is now half that of clkin:

```

create_clock -period 10.0 -name clkin [get_ports clkin]

set_propagated_clock clkin

create_clock -period [expr 10.0 / 2] -name pllout [get_pins PLL/OUT]

set propagated clock pllout

```

But there's another clock here. The divide-by 2 flop output is also a clock. It is a generated clock from pllout, with a divide-by of 2:

```

create generated clock \

-source [get pins PLL/OUT] \

-name divclk

-divide by 2

[get pins divider reg/Q]

set propagated clock divclk

Now we need to fetch the Tref and Tfb values.

set path [get_timing_paths -delay max rise \

-from [get ports clkin] \

-to [get pins PLL/CKREF] \

set ref delay [get attribute $ path arrival]

set path [get timing paths -delay max rise \

-from [get pins PLL/OUT] \

-to [get pins PLL/FB] \

set _fb_delay [get_attribute $_path arrival]

echo $ fb delay

But if we look at the result, there's a problem:

pt_shell> echo $_ref_delay

1.000000

pt shell> echo $ fb delay

pt shell>

Let's look at the timing reports for the fb path.

```

```

pt shell> set timing report unconstrained paths true

pt_shell> report_timing -delay max_rise -from [get_pins PLL/OUT] -to

[get pins PLL/FB]

**********

Report : timing

-path full

-delay max rise

-max paths 1

Design : idcm pll example

Version: V-2004.06

*********

No Paths.

```

The path no longer exists. That's because the divider flop is breaking the path.

#### Try again with just the pll FB pin endpoint:

```

pt shell> report timing -delay max rise

-to [get pins PLL/FB]

********

Report : timing

-path full

-delay max_rise

-max paths 1

Design : idcm pll example

Version: V-20\overline{0}4.0\overline{6}

*********

Startpoint: divider_reg/Q

(clock source 'divclk')

Endpoint: PLL/FB (internal pin)

Path Group: (none)

Path Type: max

Incr

______

1.82 1.82 r

0.00 1.82 r

2.20 H 4.02 r

0.10 H 4.12 r

1.00 H 5.12 r

0.00 5.12 r

clock source latency

divider reg/Q (dfnrb1)

clktree_root/Z (bufbd1)

clktree_2/Z (bufbd1)

fbdelay\(\bar{Z}\) (bufbd1)

PLL/FB (DUMMYPLL)

5.12

data arrival time

______

(Path is unconstrained)

```

## But is this correct? Let's see where the "clock source latency" comes from:

```

pt shell> report timing -delay max rise -from [get pins divider reg/CP]

to [get pins divider reg/Q]

******

Report : timing

-path full

-delay max_rise

-max paths 1

Design : idcm_pll_example

Version: V-20\overline{0}4.0\overline{6}

*********

Startpoint: divider reg

(rising edge-triggered flip-flop clocked by pllout)

Endpoint: divider reg/Q

(internal pin)

Path Group: (none)

Path Type: max

Incr Path

Point

1.50 1.50

0.00 1.50 r

0.32 1.82 r

clock network delay (propagated)

divider reg/CP (dfnrb1)

divider_reg/Q (dfnrb1)

data arrival time

1.82

______

(Path is unconstrained)

```

```

pt_shell> report_timing -delay max_rise -from [get_pins PLL/OUT] -to [get_pins

divider reg/CP] -input pins

******

Report : timing

-path full

-delay max rise

-input pins

-max paths 1

Design : idcm pll example

Version: V-20\overline{0}4.0\overline{6}

*********

Startpoint: PLL/OUT (clock source 'pllout')

Endpoint: divider reg/CP

(internal pin)

Path Group: (none)

Path Type: max

clock source latency

0.00

0.00

PLL/OUT (DUMMYPLL)

0.00

0.00 r

clktree_2x/I (bufbd1)

0.00

0.00 r

clktree_2x/Z (bufbd1)

1.50 *

1.50 r

divider_reg/CP (dfnrb1)

0.00

1.50 r

data arrival time

1.50

data arrival time

(Path is unconstrained)

```

So, the source latency of 1.82 is the prop delay from the PLL/OUT pin to the divider\_reg/CP pin (1.50) plus the CP->Q rise delay through the divider flop (0.32). That's correct.

We can see this more clearly if we use -path\_type full\_clock\_expanded with just the endpoint:

```

pt shell> report timing -delay max rise -to [get pins PLL/FB] -path type

full clock expanded

Report : timing

-path full_clock_expanded

-delay max_rise

-max paths 1

Design : idcm_pll_example

Version: V-20\overline{0}4.0\overline{6}-SP1

Startpoint: divider_reg/Q

(clock source 'divclk')

Endpoint: PLL/FB (internal pin)

Path Group: (none)

Path Type: max

Point

Path

Incr

PLL/OUT (DUMMYPLL) clktree_2x/Z (bufbd1)

divider reg/Q (dfnrb1) (gclock source)

0.32 H

-2.30 r

divider reg/Q (dfnrb1)

0.00

-2.30 r

2.20 H -0.10 r

clktree_root/Z (bufbd1)

0.10 H 0.00 r

1.00 H 1.00 r

0.00 1.00 r

1.00

clktree_2/Z (bufbd1)

fbdelay/Z (bufbd1)

PLL/FB (DUMMYPLL)

data arrival time

______

(Path is unconstrained)

```

So, let's try the fb delay code without the –from switch:

```

set _path [get_timing_paths -delay max_rise \

-to [get_pins PLL/FB] \

]

set fb delay [get attribute $ path arrival]

```

#### And the value is now correct:

```

pt_shell> echo $_fb_delay

5.120000

pt shell>

```

If a simple "-to" is too open-ended for your taste, it turns out that you also get the correct result when you do "-from [get\_pins divider\_reg/Q]", like this:

```

set _path [get_timing_paths -delay max_rise \

-from [get_pins divider_reg/Q] \

-to [get_pins PLL/FB] \

]

set _fb_delay [get_attribute $_path arrival]

pt_shell> echo $_fb_delay

5.120000

pt shell>

```

Now we can apply the source latency as before:

```

# Set the source latency

set_clock_latency -source \

[expr $_ref_delay - $_fb_delay] \

[get_clocks pllout]

```

The resulting latency should be -4.12 (1.0 - 5.12):

|        | Min Cor   | dition  | Source L | atency | Max Cor   | ndition | Source L | atency |         |

|--------|-----------|---------|----------|--------|-----------|---------|----------|--------|---------|

| Object | Early_r E | Carly_f | Late_r   | Late_f | Early_r E | Early_f | Late_r   | Late_f | Rel_clk |

| pllout | -4.12     | -4.12   | -4.12    | -4.12  | -4.12     | -4.12   | -4.12    | -4.12  |         |

| divclk | 1.82      | 1.82    | 1.82     | 1.82   | 1.82      | 1.82    | 1.82     | 1.82   |         |

Looks right.

The verify code will similarly have to change (remove the –from from the fb path or replace with the –from the divider\_reg):

```

# Verify

# Get the new fb path delay

set path [get timing paths -delay max rise \

-to [get pins PLL/FB] \

set new fb delay [get attribute $ path arrival]

# Get the ref clock delay

set path [get_timing paths -delay max rise \

-from [get ports clkin] \

-to [get pins PLL/CKREF] \

set new ref delay [get attribute $ path arrival]

set diff [expr $ new ref delay - $ new fb delay]

if { ($ diff > 0.01) | | ($ diff < -0.01)

} {

echo "Error: Difference between FB and REF pins out of range!"

echo " _new_ref_delay is $_new_ref_delay"

echo " new fb delay is $_new_ref_delay"

echo " _new_fb_delay is $_new_fb_delay"

} else {

echo "PLL timing verified!"

And the verify works:

PLL timing verified!

Apply the i/o constraints as before:

set input delay -max 8.0 -clock clkin [get ports din]

set input delay -min 0.5 -clock clkin [get ports din]

set output delay -max 2.0 -clock clkin [get ports dout]

set output delay -min [expr -1.0 * 0.5] -clock clkin [get ports dout]

Now let's look at some i/o timing:

pt shell> report timing -input pins -path type full clock expanded -from din

Report : timing

-path full clock expanded

-delay max

-input pins

-max paths 1

Design : idcm pll example

Version: V-20\overline{0}4.0\overline{6}

********

```

21

```

Startpoint: din (input port clocked by clkin)

Endpoint: dout_reg (rising edge-triggered flip-flop clocked by divclk)

Path Group: divclk

Path Type: max

```

| Point                                                                                                                                                                                           | Incr                 | Path                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|

| clock clkin (rise edge) clock network delay (propagated) input external delay din (in) dinpad/I (bufbd1) dinpad/Z (bufbd1) dout_reg/D (dfnrb1) data arrival time                                | 0.00<br>8.00<br>0.00 | 8.00 r                                                |

| <pre>clock divclk (rise edge) clock pllout (source latency) PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) divider_reg/CP (dfnrb1) divider_reg/Q (dfnrb1) (gclock source)</pre> | 0.00                 | 10.00<br>5.88<br>5.88 r<br>5.88 r<br>7.38 r<br>7.38 r |

| <pre>clktree_root/I (bufbd1) clktree_root/Z (bufbd1) clktree_1/I (bufbd1) clktree_1/Z (bufbd1) dout_reg/CP (dfnrb1) library setup time data required time</pre>                                 | 0.00<br>2.20 *       | 10.20 r                                               |

| data required time data arrival time                                                                                                                                                            |                      | 10.12<br>-9.20                                        |

| slack (MET)                                                                                                                                                                                     |                      | 0.92                                                  |

Notice that the slack is exactly the same as it was with the earlier non-multiplying idc pll example. This is to be expected. I made the pll run at 2x, but then clocked dout\_reg with the divide-by 2 clock, so nothing changed relative to the i/o timing. Extra delay in the clock path (the divider) is just "insertion delay" and gets cancelled out by the pll.

## The same is true of the dout path:

22

```

Startpoint: dout reg (rising edge-triggered flip-flop clocked by divclk)

Endpoint: dout (output port clocked by clkin)

Path Group: clkin

Path Type: max

clock divclk (rise edge)

0.00

0.00

clock pllout (source latency)

-4.12

-4.12

PLL/OUT (DUMMYPLL)

0.00

-4.12 r

clktree_2x/I (bufbd1)

0.00

-4.12 r

clktree_2x/Z (bufbd1)

1.50 * -2.62 r

divider_reg/CP (dfnrb1)

0.00

-2.62 r

clktree_2x/Z (bufbd1)

divider_reg/CP (dfnrb1)

divider_reg/Q (dfnrb1) (gclock source)

0.32 * -2.30 r

0.00 -2.30 r

2.20 * -0.10 r

0.00 -0.10 r

0.30 * 0.20 r

0.00 0.20 r

0.32 * 0.52 r

0.00 0.52 r

2.50 * 3.02 r

0.00 3.02 r

clktree root/I (bufbd1)

clktree_root/Z (bufbd1)

clktree_1/I (bufbd1)

clktree 1/Z (bufbd1)

dout reg/CP (dfnrb1)

dout_reg/Q (dfnrb1)

doutpad/I (bufbd1) doutpad/Z (bufbd1)

dout (out)

data arrival time

3.02

clock clkin (rise edge) 10.00 10.00 clock network delay (propagated) 0.00 10.00 output external delay -2.00 8.00

data required time

_____

data required time

data arrival time

slack (MET)

```

## 2.5 The PLL model itself

Up to this point, I haven't talked about the model of the PLL itself. In the examples above, the model was an "empty shell" like this:

```

module DUMMYPLL (

OUT,

FB,

CKREF

);

output OUT;

input CKREF;

input FB;

```

endmodule

It could also have been allowed to default to a "black box" by Primetime. The results would be the same.

This works fine if the flow uses SDF, but with parasitics this isn't sufficient. When using parasitics, Primetime needs to know more about the driving and load characteristics of the PLL itself. This requires a model of the PLL itself, which can be a bit tricky. This is covered in appendix 10.1 If you're using parasitics, please read this appendix carefully.

## 2.6 Performance considerations

Recall that the basic flow outlined above was:

- 1. Create all the clocks, including the pll output clock (but don't set the source latency yet).

- 2. Get Tref and Tfb using get\_timing\_paths.

- 3. Calculate the source latency (Tref Tfb) and apply it to the pll output clock. The source latency value will usually be negative.

- 4. Use set\_input\_delay and set\_output\_delay with the reference clock to specify the i/o timing.

- 5. Allow the clocks to time against each other (don't do set false path between them)

And we could add another:

6. Run the verify code to ensure that the arrival time at CKREF matches the arrival time at FB.

The drawback to this is performance. Steps 2 and 6 cause timing updates. Once you have confidence in the flow, you could always turn off step 6. But step 2 always causes a timing update.

That's not a big problem if you only have 1 pll. But if you have several, you'll want to structure the code such that step 1 covers all clocks of all PLLs, step 2 fetches all Tref and Tfb values for all pll, etc. The code is much harder to read, but the performance impact can be very noticeable.

## 3 Duty Cycle

The term duty cycle refers to the percent of time that the clock signal is high. It matters when signals are sampled on the falling edge of the clock. We will examine two cases: internal clocks and primary input clocks / plls.

## 3.1 Internal clocks (other than PLLs)

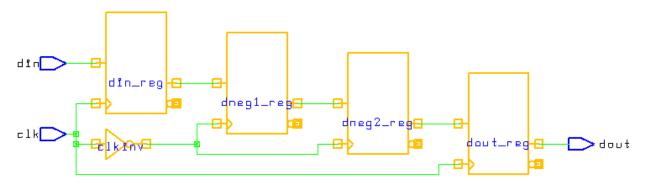

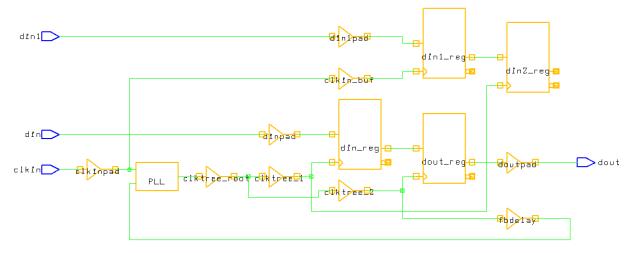

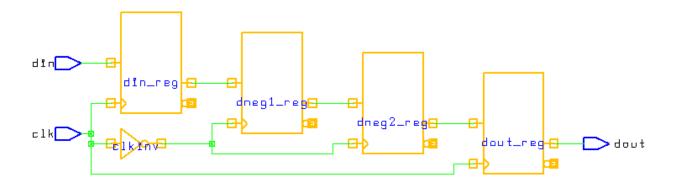

It is important to note that PT will handle the duty cycle calculations without user intervention for most internally-generated clocks. For example, take the 2x multiplier pll circuit shown above and add another flop in the data path. The first flop (din\_reg) will be clocked by the pll divide-by 2 output as before. But the second flop (dout\_reg) will be clocked by an inverted version of this clock.

Figure 3-1

The script to handle this is exactly the same as before. To illustrate the effect, I will force the rise and fall delays of the divider\_reg to be different:

```

set_annotated_delay -cell -from divider_reg/CP -to divider_reg/Q -rise 0.32

set annotated delay -cell -from divider reg/CP -to divider reg/Q -fall 0.20

```

Since the signal falls more quickly than it rises, the high time will by reduced.

Now, report the timing between the 2 flops:

Startpoint: din\_reg (rising edge-triggered flip-flop clocked by divclk)

Endpoint: dout\_reg (rising edge-triggered flip-flop clocked by divclk')

Path Group: divclk

Path Type: max

| Point                                                                                                                                                                                            | Incr                                               | Path                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------|

| clock divclk (rise edge) clock pllout (source latency) PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) divider_reg/CP (dfnrb1) divider_reg/Q (dfnrb1) (gclock source)             | -4.12<br>0.00<br>0.00                              | 0.00<br>-4.12<br>-4.12 r<br>-4.12 r<br>-2.62 r<br>-2.62 r                |

| clktree_root/I (bufbd1) clktree_root/Z (bufbd1) clktree_1/I (bufbd1) clktree_1/Z (bufbd1) din_reg/CP (dfnrb1) din_reg/CP (dfnrb1) din_reg/Q (dfnrb1) <- dout_reg/D (dfnrb1) data_arrival_time    | 0.32 * 0.00 2.20 * 0.00 0.30 * 0.00 0.00 0.32 0.00 | -0.10 r                                                                  |

| <pre>clock divclk' (rise edge) clock pllout (source latency) PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) divider_reg/CP (dfnrb1) divider_reg/Q (dfnrb1) (gclock source)</pre> | 5.00<br>-4.12<br>0.00<br>0.00<br>1.50 *<br>0.00    | 5.00<br>0.88<br>0.88 r<br>0.88 r<br>2.38 r<br>2.38 r                     |

| <pre>clktree_root/I (bufbd1) clktree_root/Z (bufbd1) clktree_inv/I (inv0d2) clktree_inv/ZN (inv0d2) dout_reg/CP (dfnrb1) library setup time data required time</pre>                             | 0.20 * 0.00 2.20 * 0.00 0.03 0.00 -0.08            | 2.58 f<br>2.58 f<br>4.78 f<br>4.78 f<br>4.81 r<br>4.81 r<br>4.73<br>4.73 |

| data required time data arrival time                                                                                                                                                             |                                                    | 4.73<br>-0.52                                                            |

| slack (MET)                                                                                                                                                                                      |                                                    | 4.21                                                                     |

A couple of things to notice about this trace. First, the capture edge is divclk` at time 5.0. The refclk period is 10.0. We're running the pll as a 2x multiplier, so its period is 5.0. These flops are on the div\_clk, which is divide-by-2 on the pll – which gives it a period of 10.0. So the fall edge of divclk is at 5.0 – we're timing a half-cycle path.

The second thing to notice is that the capture clock uses the *fall* edge through divider\_reg/CP->Q. Since this is set to 0.20 (instead of 0.32 for the rise edge), the capture clock will occur 0.12ns sooner. This reflects the non-ideal duty cycle of the generated clock. The effect will be to reduce the slack on this rise-to-fall path.

The important thing to notice, however, is that the duty cycle effect is handled automatically by the tool.

## 3.2 Primary input clocks and PLLs

Primary input clocks and pll output clocks are *not* handled automatically by the tool, since it can't deduce what the effect would be. You have to tell it via the –waveform option on create\_clock. But there's a snag. The incoming clock (or the pll output clock) spec doesn't tell you that the duty cycle is, say, "55%". It usually says the duty cycle is, say, 50% +/- 5%. For internal clocks, the duty cycle is what it is, but for primary input clocks and pll output clocks, it's a range.

Let's take this simple example:

Figure 3-2

This circuit has paths from the rising clock to the falling clock, from the falling clock to the falling clock, and from the falling clock to the rising clock.

So, how do we model this in PrimeTime? Well, duty cycle seems like an uncertainty, so your first thought might be to use set\_clock\_uncertainty. Unfortunately, this command doesn't allow you to set uncertainty between the rising and falling edges *of the same clock*. It has the –rise\_to, -fall\_from options, but the man page says you can only use this for *inter-clock* uncertainty – that is, uncertainty between two clocks.

| <ad< th=""><th><u>lded</u></th><th>3/17</th><th><u>/2005&gt;</u></th><th></th></ad<> | <u>lded</u> | 3/17 | <u>/2005&gt;</u> |  |

|--------------------------------------------------------------------------------------|-------------|------|------------------|--|

|                                                                                      |             | •    |                  |  |

| The man page says:                       |

|------------------------------------------|

| -from from_clock -to to_clock            |

| These two options specify the source and |

| destination clocks for interclock        |

| uncertainty. You must specify either     |

| the pair of -from/-rise_from/-fall_from  |

| and -to/-rise_to/-fall_to, or            |

| object_list; you cannot specify both.    |

|                                          |

Formatte

| <br>-fall | <b>Indicates that uncertainty applies to</b> |

|-----------|----------------------------------------------|

|           | only the falling edge of the destination     |

|           | clock. By default, the uncertainty           |

|           | applies to both rising and falling           |

|           | edges. This option is valid only for         |

|           | interclock uncertainty, and is now           |

|           | obsolete. Unless you need this option        |

|           | for backward-compatibility, use -fall_t      |

|           | instead.                                     |

Sure enough, if you try to use edge switches with intraclock uncertainty, you get an error:

```

pt shell> set_clock_uncertainty -setup -rise 0.2 [get_clocks clkin]

Error: Cannot specify '-rise or -fall' with 'clock_list'. (CMD-001)

0

```

#### But PT will accept this:

```

pt_shell> set_clock_uncertainty -setup -rise_from [get_clocks clkin] -fall_to [get_clocks clkin] 0.2

```

So, it appears that you *can* specify single-edge uncertainty intra-clock by using the inter-clock syntax. The man page doesn't *say*, you *can't* make both clocks in the inter-clock syntax be the same.

#### It appears to work:

```

pt shell> report timing -from din reg -to dout reg

************

Report : timing

-path full

-delay max

-max paths 1

Design : simple

Version: W-2004.12-SP1

Date : Thu Mar 17 18:26:54 2005

***********

Warning: There are 3 invalid start points. (UITE-416)

Warning: There are 2 invalid end points for constrained paths. (UITE-416)

Startpoint: din reg (rising edge-triggered flip-flop clocked by clkin)

Endpoint: dout reg (rising edge-triggered flip-flop clocked by clkin')

Path Group: clkin

Path Type: max

Path

Incr

Point

```

Formatte

Formatte

| clock clkin (rise edge)          | 0.00  | 0.00   |  |

|----------------------------------|-------|--------|--|

| clock network delay (propagated) | 0.00  | 0.00   |  |

| din reg/CP (dfnrb1)              | 0.00  | 0.00 r |  |

| din reg/Q (dfnrb1) <-            | 0.31  | 0.31 r |  |

| dout reg/D (dfnrb1)              | 0.00  | 0.31 r |  |

| data arrival time                |       | 0.31   |  |

|                                  |       |        |  |

| clock clkin' (rise edge)         | 5.00  | 5.00   |  |

| clock network delay (propagated) | 0.02  | 5.02   |  |

| inter-clock uncertainty          | -0.20 | 4.82   |  |

| dout reg/CP (dfnrb1)             |       | 4.82 r |  |

| library setup time               | -0.09 | 4.73   |  |

| data required time               |       | 4.73   |  |

|                                  |       |        |  |

| data required time               |       | 4.73   |  |

| data arrival time                |       | -0.31  |  |

|                                  |       |        |  |

| slack (MET)                      |       | 4.42   |  |

Still, there are disadvantages to this approach. Rolling the duty cycle into uncertainty will make it difficult to separate duty cycle issues from other uses of set clock uncertainty described later.

On the other hand, the uncertainty method may have some advantages in runtime (fewer clocks) and possibly in SI analysis over the technique described below.

It is possible to model duty cycle using "set\_clock\_latency -fall", but it doesn't work out-of-the-box. You have to (ab)use some of the on-chip-variation features for something unrelated to on-chip-variation, and isn't too clean (it is explained in Appendix [10.3/4]).

Until a few years ago, there seemed to be no really clean way to model this except to run the script twice – once for each of the extreme duty cycle waveforms (I call them min\_high and max\_high). With the introduction of multiclock propagation capabilities in PT, we can now do this in a single run.

Since we are going to use multiclock propagation, we first need to turn it on (it's off by default):

```

set timing enable multiple clocks per reg true

```

Formatte Norwegian Formatte

**Formatte**

Formatte

Now we can create the two clocks. I have defined a single variable "\_duty\_cycle\_min" to specify what the minimum high period can be. I'll set "\_duty\_cycle\_max" to 1.0 minus this value (but you could set it to some other value if you wanted to):

```

set _period 10.0

set _duty_cycle_min 0.40

set _duty_cycle_max [expr 1.0 - $_duty_cycle_min]

create_clock -period $_period -name clk_minhigh \

-waveform [list 0 [expr $_period * $_duty_cycle_min]] \

[get_ports clk]

set_propagated_clock clk_minhigh

create_clock -period $_period -name clk_maxhigh \

-waveform [list 0 [expr $_period * $_duty_cycle_max]] \

-add \

[get_ports clk]

set_propagated_clock clk_maxhigh

```

Notice the use of "-add" on the second create\_clock. This is necessary to have both clocks exist on the same pin.

Now, these clocks can never exist at the same time, so we don't want them timing against one another. We could do set\_false\_path from each to the other, but instead let's use the new set\_clock\_groups command. The two clocks can never coexist, so I'll use the –exclusive option:

```

set_clock_groups -exclusive \

-group {clk_minhigh} \

-group {clk_maxhigh}

```

Now let's look at the timing reports. We'll time the path from the din\_reg to the dneg1\_reg first:

Startpoint: din\_reg (rising edge-triggered flip-flop clocked by clk\_maxhigh)

Endpoint: dneg1\_reg (rising edge-triggered flip-flop clocked by

clk\_maxhigh')

Path Group: clk\_maxhigh

Path Type: max

| Point                                                                                                                                                                    | Incr                                                    | Path                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------|

| <pre>clock clk_maxhigh (rise edge) clock source latency clk (in) din_reg/CP (dfnrb1) din_reg/Q (dfnrb1) &lt;- dneg1_reg/D (dfnrb1) data arrival time</pre>               |                                                         |                                      |

| <pre>clock clk_maxhigh' (rise edge) clock source latency clk (in) clkinv/I (inv0d2) clkinv/ZN (inv0d2) dneg1_reg/CP (dfnrb1) library setup time data required time</pre> | 6.00<br>0.00<br>0.00<br>0.00<br>1.00 *<br>0.00<br>-0.09 | 6.00 f<br>6.00 f<br>7.00 r<br>7.00 r |

| data required time<br>data arrival time                                                                                                                                  |                                                         | 6.91<br>-0.31                        |

| slack (MET)                                                                                                                                                              |                                                         | 6.60                                 |

Startpoint: din\_reg (rising edge-triggered flip-flop clocked by clk\_minhigh)

Endpoint: dneg1 reg (rising edge-triggered flip-flop clocked by

clk minhigh')

Path Group: clk minhigh

Path Type: max

| Point                                                                                                                                                                    | Incr                   | Path                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|

| clock clk_minhigh (rise edge) clock source latency clk (in) din_reg/CP (dfnrb1) din_reg/Q (dfnrb1) <- dneg1_reg/D (dfnrb1) data arrival time                             | 0.00<br>0.31 *         |                          |

| <pre>clock clk_minhigh' (rise edge) clock source latency clk (in) clkinv/I (inv0d2) clkinv/ZN (inv0d2) dneg1_reg/CP (dfnrb1) library setup time data required time</pre> | 0.00<br>1.00 *<br>0.00 | 4.00<br>4.00 f<br>4.00 f |

| data required time<br>data arrival time                                                                                                                                  |                        | 4.91<br>-0.31            |

| slack (MET)                                                                                                                                                              |                        | 4.60                     |

We get two timing reports – one for clk\_minhigh and one for clk\_maxhigh. Since we are launching data from a rising edge (both clocks have the same rising edge waveform) and capturing with the falling edge, the worst case for setup is the shorter duty cycle clock – clk\_minhigh. As you can see, clk\_minhigh does indeed have less slack. Its fall edge (that weird "clock clk\_minhigh" (rise edge)" is PT-speak for falling edge) is at time 4.0 – 40% of the 10ns period.

Next we'll look at the falling-edge to falling-edge path.

```

pt shell> report timing -input pins -path type full clock -from dneq1 reg -to

dneg2 reg

*****

Report : timing

-path full clock

-delay max

-input pins

-max paths 1

Design : duty cycle piclk

Version: V-2004.06

Startpoint: dneg1 reg (rising edge-triggered flip-flop clocked by

clk maxhigh')

Endpoint: dneg2 reg (rising edge-triggered flip-flop clocked by

clk maxhigh')

Path Group: clk maxhigh

Path Type: max

Point

clock clk_maxhigh' (rise edge)

6.00

6.00

clock source latency

0.00

6.00

clk (in)

0.00

6.00 f

clkinv/I (inv0d2)

0.00

6.00 f

clkinv/ZN (inv0d2)

1.00 *

7.00 r

dneg1_reg/CP (dfnrb1)

0.00

7.00 r

dneg1_reg/Q (dfnrb1) <-</td>

0.32 *

7.32 r

dneg2_reg/D (dfnrb1)

0.00

7.32 r

data arrival time

7.32

clock clk_maxhigh' (rise edge)

16.00

16.00

clock source latency

0.00

16.00

clk (in)

0.00

16.00 f

clkinv/I (inv0d2)

0.00

16.00 f

clkinv/ZN (inv0d2)

1.00 *

17.00 r

dneg2_reg/CP (dfnrb1)

0.00

17.00 r

library setup time

-0.09

16.91

data required time

data required time

data arrival time

9.59

slack (MET)

```

```

Startpoint: dneg1 reg (rising edge-triggered flip-flop clocked by

clk minhigh')

Endpoint: dneg2 reg (rising edge-triggered flip-flop clocked by

clk_minhigh')

Path Group: clk minhigh

Path Type: max

Point

clock clk minhigh' (rise edge) 4.00 4.00

9e) 4.00 4.00

0.00 4.00

0.00 4.00 f

0.00 4.00 f

1.00 * 5.00 r

0.00 5.00 r

0.32 * 5.32 r

0.00 5.32 r

clock source latency

clk (in)

clkinv/I (inv0d2)

clkinv/ZN (inv0d2)

dneg1 reg/CP (dfnrb1)

dneg1_reg/@ (dfnrb1) <-

dneg2_reg/D (dfnrb1)</pre>

dneg2 reg/D (dfnrb1)

data arrival time

5.32

```

| <pre>clock clk_minhigh' (rise edge) clock source latency clk (in) clkinv/I (inv0d2) clkinv/ZN (inv0d2) dneg2_reg/CP (dfnrb1) library setup time data required time</pre> | 14.00<br>0.00<br>0.00<br>0.00<br>1.00 *<br>0.00<br>-0.09 | 14.00<br>14.00<br>14.00 f<br>14.00 f<br>15.00 r<br>15.00 r<br>14.91<br>14.91 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|

| data arrival time                                                                                                                                                        |                                                          | 14.91<br>-5.32                                                               |

-----

Again, there are two traces, one for each clock. Although the launch and capture times are different, as you would expect, the slack values are the same.

9.59

Now let's look at the dneg2 reg to dout reg path:

slack (MET)

| Point                                                                                                                                                                                               | Incr                                                             | Path          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|

| <pre>clock clk_maxhigh' (rise edge) clock source latency clk (in) clkinv/I (inv0d2) clkinv/ZN (inv0d2) dneg2_reg/CP (dfnrb1) dneg2_reg/Q (dfnrb1) &lt;- dout_reg/D (dfnrb1) data arrival time</pre> | 6.00<br>0.00<br>0.00<br>0.00<br>1.00 *<br>0.00<br>0.32 *<br>0.00 | 7.00 r        |

| <pre>clock clk_maxhigh (rise edge) clock source latency clk (in) dout_reg/CP (dfnrb1) library setup time data required time</pre>                                                                   | 10.00<br>0.00<br>0.00<br>0.00<br>-0.10                           |               |

| data required time data arrival time                                                                                                                                                                |                                                                  | 9.90<br>-7.32 |

| slack (MET)                                                                                                                                                                                         |                                                                  | 2.58          |

Since this is from the falling edge to the rising edge, the worst case path will be from the later falling edge, which is clk\_maxhigh. There is another trace for clk\_minhigh with 2 more ns of slack.

So, we can model duty cycle variation in a single pass using two "exclusive" clocks and multiclock propagation.

## 3.3 Applying this to our multiplier pll circuit

We can use this on our multiplier pll circuit in 2 places – the primary input clock clkin and the pll clock pllout.

We'll use the same circuit as before, except that I have added a pair of flops on the pllout clock, one rising edge and the other falling edge, to illustrate the duty cycle effect on pllout clock.

Figure 3-3

First we'll create the primary input clocks, one for each duty cycle case. We'll use a loop.

```

set _period 10.0

set _duty_cycle(min) 0.40

set _duty_cycle(max) [expr 1.0 - $_duty_cycle(min)]

foreach _dc {min max} {

create_clock -period $_period -name clkin_${_dc}high \

-waveform [list 0 [expr $_period * $_duty_cycle($_dc)]] \

-add \

[get_ports clkin]

set_propagated_clock clkin_${_dc}high

}

set_clock_groups -exclusive \

-group {clkin_minhigh} \

-group {clkin_minhigh}

```

Notice the "-add" switch again. Since the create\_clock is done in a loop, the –add will occur on both create\_clock commands, including the first one. This is harmless.

Creating the pll output clocks is similar:

```

set _period [expr 10.0 / 2]

set _duty_cycle(min) 0.40

set _duty_cycle(max) [expr 1.0 - $_duty_cycle(min)]

foreach _dc {min max} {

create_clock -period $_period -name pllout_${_dc}high \

-waveform [list 0 [expr $_period * $_duty_cycle($_dc)]] \

-add \

[get_pins PLL/OUT]

set_propagated_clock pllout_${_dc}high

}

set_clock_groups -exclusive \

-group {pllout_minhigh} \

-group {pllout_maxhigh}

```

Now we need to create the generated divider clock. But now there are two clocks feeding the divider\_reg/CP pin. Which do we choose, and how do we tell PT about our choice?

Well, in this case, the choice is arbitrary. Since divider\_reg only runs on rising edges, it doesn't matter which pllout\_ clock we choose. If divider\_reg ran on falling edges, however, we would have to create two generated clocks – one for pllout\_minhigh and one for pllout\_maxhigh. We would then add these to their respective clock groups in set\_clock\_group. In fact, we could still do this even though divider\_reg runs on rising edges – the propagated clocks would be identical, but this is harmless. Some would argue that this is more consistent. It's is a personal choice.

To keep things simple, we'll just create one generated clock. We'll use pllout\_maxhigh.

When multiple clocks feed into a point where we want to create a generated clock, it is necessary to tell PT which clock is the source. This is done using the "-master" switch. To use the "-master" switch, you must also use the "-add" switch, even though we're only creating one clock.

```

create_generated_clock \

-source [get_pins PLL/OUT] \

-name divclk \

-divide_by 2 \

-add \

-master pllout_maxhigh \

[get_pins divider_reg/Q]

set propagated clock divclk

```

The code to fetch the Tref and Tfb values is unchanged:

```

set _path [get_timing_paths -delay max_rise \

-from [get_ports clkin] \

-to [get_pins PLL/CKREF] \

]

set _ref_delay [get_attribute $_path arrival]

set _path [get_timing_paths -delay max_rise \

-from [get_pins divider_reg/Q] \

-to [get_pins PLL/FB] \

]

set _fb delay [get_attribute $ path arrival]

```

Now to set the source latency. There are two pll output clocks now, and they need the same latency value. So, we do it in a loop again:

```

foreach _dc {minhigh maxhigh} {

set_clock_latency -source \

[expr $_ref_delay - $_fb_delay] \

[get_clocks pllout_${_dc}]

}

```

Now we'll set the i/o timing. Since we now have two versions of clkin, we'll have to create an input/output constraint for each. Also, I want to illustrate the duty cycle effects here. In this case, the duty cycle is on the external clock clkin, so I'll do the i/o constraints relative to the falling edge.

```

foreach _dc {minhigh maxhigh} {

set_input_delay -max 4.0 -clock clkin_${_dc} -clock_fall -add [get_ports

din]

set_input_delay -min 0.5 -clock clkin_${_dc} -clock_fall -add [get_ports

din]

set_output_delay -max 1.0 -clock clkin_${_dc} -clock_fall -add [get_ports

dout]

set_output_delay -min [expr -1.0 * 0.5] -clock clkin_${_dc} -clock_fall -add

[get_ports dout]

}

```

Now look at the timing from din:

```

Startpoint: din (input port clocked by clkin_maxhigh)

Endpoint: dout_reg (rising edge-triggered flip-flop clocked by divclk)

Path Group: divclk

Path Type: max

```

| Point                                                                                                                                                                    | Incr                                 | Path                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------|

| clock clkin_maxhigh (fall edge) clock network delay (propagated) input external delay din (in) dinpad/I (bufbd1) dinpad/Z (bufbd1) dout_reg/D (dfnrb1) data arrival time | 0.00<br>4.00<br>0.00<br>0.00<br>1.20 | 6.00<br>6.00<br>10.00 r<br>10.00 r<br>10.00 r<br>* 11.20 r<br>11.20 r<br>11.20 r   |

| <pre>clock divclk (rise edge) clock pllout_maxhigh (source latency)</pre>                                                                                                | 10.00                                |                                                                                    |

| PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) divider_reg/CP (dfnrb1) divider_reg/Q (dfnrb1) (gclock source)                                            | 0.00<br>0.00<br>1.50<br>0.00         | 5.88<br>5.88 r<br>5.88 r<br>* 7.38 r<br>7.38 r                                     |

| <pre>clktree_root/I (bufbd1) clktree_root/Z (bufbd1) clktree_1/I (bufbd1) clktree_1/Z (bufbd1) dout_reg/CP (dfnrb1) library setup time data required time</pre>          | 0.00<br>2.20<br>0.00<br>0.30         | * 7.70 r<br>7.70 r<br>* 9.90 r<br>9.90 r<br>* 10.20 r<br>10.20 r<br>10.12<br>10.12 |

| data required time data arrival time                                                                                                                                     |                                      | 10.12<br>-11.20                                                                    |

| slack (VIOLATED)                                                                                                                                                         |                                      | -1.08                                                                              |

I have nworst defaulted to 1, so the report only shows the worst case – data launched by clkin\_maxhigh (latest possible falling edge of clkin) and captured by divclk. If I set nworst to 4, I'd see the clkin minhigh paths as well.

#### Now let's look at the pllout path:

Endpoint: d2xinv\_reg (rising edge-triggered flip-flop clocked by pllout\_maxhigh')

Path Group: pllout\_maxhigh

Path Type: max

| Point                                                                                                                                                                                                                                            | Incr                                                                     | Path                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| <pre>clock pllout_maxhigh (rise edge) clock source latency PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) d2x_reg/CP (dfnrb1) d2x_reg/Q (dfnrb1) &lt;- d2xinv_reg/D (dfnrb1) data arrival time</pre>                             | 0.00<br>-4.12<br>0.00<br>0.00<br>1.50 *<br>0.00<br>0.34<br>0.00          | -4.12 r<br>-2.62 r                                                                          |

| <pre>clock pllout_maxhigh' (rise edge) clock source latency PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) clktree_2xinv/I (inv0d2) clktree_2xinv/ZN (inv0d2) d2xinv_reg/CP (dfnrb1) library setup time data required time</pre> | 3.00<br>-4.12<br>0.00<br>0.00<br>1.50 *<br>0.00<br>0.04<br>0.00<br>-0.08 | 3.00<br>-1.12<br>-1.12 f<br>-1.12 f<br>0.38 f<br>0.38 f<br>0.42 r<br>0.42 r<br>0.33<br>0.33 |

| data required time data arrival time                                                                                                                                                                                                             |                                                                          | 0.33                                                                                        |

| slack (MET)                                                                                                                                                                                                                                      |                                                                          | 2.61                                                                                        |

Startpoint:  $d2x_reg$  (rising edge-triggered flip-flop clocked by pllout\_minhigh)

Endpoint: d2xinv\_reg (rising edge-triggered flip-flop clocked by pllout minhigh')

Path Group: pllout\_minhigh

Path Type: max

| Point                                                                                                                                                                                                      | Incr                                                            | Path                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|

| clock pllout_minhigh (rise edge) clock source latency PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) d2x_reg/CP (dfnrb1) d2x_reg/Q (dfnrb1) <- d2xinv_reg/D (dfnrb1) data arrival time     | 0.00<br>-4.12<br>0.00<br>0.00<br>1.50 *<br>0.00<br>0.34<br>0.00 | -4.12 r<br>-4.12 r<br>-4.12 r<br>-2.62 r<br>-2.62 r<br>-2.28 r |

| <pre>clock pllout_minhigh' (rise edge) clock source latency PLL/OUT (DUMMYPLL) clktree_2x/I (bufbd1) clktree_2x/Z (bufbd1) clktree_2xinv/I (inv0d2) clktree_2xinv/ZN (inv0d2) d2xinv_reg/CP (dfnrb1)</pre> | 2.00<br>-4.12<br>0.00<br>0.00<br>1.50 *<br>0.00<br>0.04<br>0.00 | -2.12<br>-2.12 f<br>-2.12 f<br>-0.62 f<br>-0.62 f<br>-0.58 r   |

| library setup time<br>data required time | -0.08 | -0.67<br>-0.67 |  |

|------------------------------------------|-------|----------------|--|

| data required time data arrival time     |       | -0.67<br>2.28  |  |

| slack (MET)                              |       | 1.61           |  |

It reports paths on both pll clocks (no need to change nworst here – there are two capture clocks instead of two launch clocks) – the worst being the capture with pllout\_minhigh because it is the nearest falling edge after launching data on the rising edge.

# 3.4 When to use these techniques

It is important to point out that you only need to create these pairs of clocks to represent duty cycle specs when you have opposite-edge clocking. If you're *sure* nothing happens on falling edges, you don't need to do all this.

### 4 Jitter

# 4.1 Jitter, skew, and uncertainty

I don't know if there are any "official" definitions of jitter and skew. I tend to think of jitter as a high-frequency, cycle-to-cycle phenomenon. I tend to think of skew as something static or at least very slow-changing. But there is one type of "skew" that I want to discuss up front – clock tree skew.

Clock tree skew is the difference in delays from the clock source to the various flop clock pins on the clock network. Because clock tree skew is often modeled in synthesis as clock uncertainty, it has come to be associated in many people's minds with all the other things that are modeled using clock uncertainty. However, for post-route analysis (which is what is being addressed in this paper), clock tree skew doesn't exist as a separate entity and does not need to be modeled. It is already there in the delay numbers or parasitics. For post-route analysis, any skew in the clock tree will automatically be handled by PT – it knows the exact delay to each element on the clock tree and will do slack calculations using these numbers. There is no need to budget for clock tree skew.

There is also a phenomenon that I would call "clock tree jitter". Since switching thresholds and delay can vary slightly according to switching activity in other gates, there may indeed be more cycle-to-cycle jitter at the end of the clock tree than there was at the beginning. I have seen this in an actual chip – a heavily loaded divide-by 2 clock was "modulating" the faster clock. Every time the slow clock switched from low to high, a lot of current was drawn, and the faster clock's edge rate would slow down, thus delaying the faster clock. This caused a fairly pronounced cycle-to-cycle jitter at the end of the fast clock tree. This is admittedly a somewhat extreme case, but we may someday have to account for "clock tree jitter" in our analysis.

# 4.2 My definition of jitter

There doesn't seem to be a common interpretation of what a jitter specification means. I'm going to define jitter somewhat loosely as follows:

"Jitter is the maximum/minimum variation in the length of a single clock cycle".

This means that a 10ns clock with jitter of +/-100ps can have a minimum cycle length of 9.9ns and a maximum cycle length of 10.1ns.

This is not the only possible definition of jitter. You can also define jitter as "the uncertainty in the location of a clock *edge* relative to its nominal location". By this definition, our 10ns clock with +/-100ps jitter can actually have a minimum period of 9.8 and a maximum period of 10.2 (jitter edge late followed by jitter edge early and jitter edge early followed by jitter edge late). Or you could define our original clock (period 9.9 to 10.1) as having *edge* jitter of +/-50ps.

These two different definitions stem from two different sources of jitter. The "cycle" definition represents "frequency" jitter – like a PLL adjusting its cycle to track a source. The "edge" definition represents "noise" jitter – switching thresholds and the like that cause uncertainty against a steady frequency.

Both types of jitter may be real. In most cases, you can convert "noise" jitter to an equivalent 2x value and add it to the "frequency" jitter to get *cycle* jitter (which is what I'm using here). Whenever you divide the clock in some way, this isn't so clean. More on this later (see the section on jitter and generated clocks later in this chapter).

## 4.3 Sources of jitter

There are several sources of jitter related to the pll:. They are:

- 1. PLL cycle-to-cycle jitter. This is the change in period of the PLL on a cycle-to-cycle basis.

- 2. Refclk cycle-to-cycle jitter. This is the change in period of the Refclk on a cycle-to-cycle basis.

- 3. PLL phase error. The job of the pll is to make the Fb pin match the Ref pin in phase and frequency. But the pll is not perfect. Depending on process, temperature, etc there may be some small difference between the arrival time at the Ref pin and at the Fb pin. Pll phase error is the measure of this difference.

Pll phase error isn't technically a form a jitter, but I have included it because it is modeled in the same way.

# 4.4 Effects of jitter on different sorts of paths

When modeling jitter effects in PT, it is important to consider the effect of different types of jitter on different paths.

First, consider the simple case of two flops on a single clock:

Figure 4-1

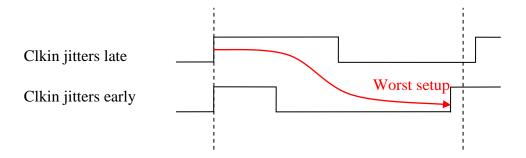

Once we select an arbitrary time zero for the first edge, here are two possibilities for the second clock edge – early and late.

Figure 4-2

It's easy to see that the worst-case setup is affected by the jitter. If the clock jitters by +/- 100ps, that means that the capture clock could be 100ps earlier or 100ps later. Later won't matter (for setup), but earlier will reduce the available clock period and therefore reduce the path slack.

Pll cycle-to-cycle jitter will not, however, affect hold paths within the PLL's clock tree. This is because hold is a "single-edge" or "same-edge" phenomenon. The question is whether a source flop will change its data too soon to avoid being captured by the capture flop *on the same edge*. If the next edge jitters, it won't affect hold.

However, hold paths *between* the pll clock and another clock (like the refclk) *will be* affected by the PLL's cycle-to-cycle jitter.

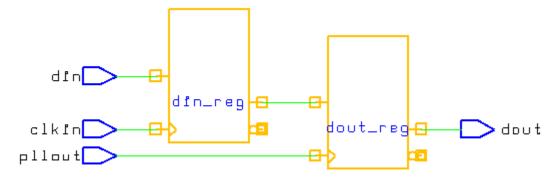

Here's an example circuit and waveforms to illustrate this:

Figure 4-3

Figure 4-4

Although the path uses clocks that are nominally the "same edge" they are really not the *same* edge. They are really edges of two different clocks that are supposed to occur at the same time. But the "at the same time" is affected by jitter. A flop clocked by the pll could in fact launch its data earlier due to the PLL's cycle-to-cycle jitter without there being any matching movement of the capture clock (refclk). It's easy to see from the above waveform that both setup and hold margins will be reduced by the *sum* of the jitters of both clocks.

Now consider pll phase error. Unlike jitter, pll phase error doesn't affect edge-to-edge timing at all. It is simply a time shift relative to some arbitrary external standard. Thus, it has absolutely no effect on internal paths within the PLL's clock tree. If the pll clock is shifted from the refclk by 100ps or 100seconds, it won't matter to flops along the PLL's clock tree for either setup or hold.

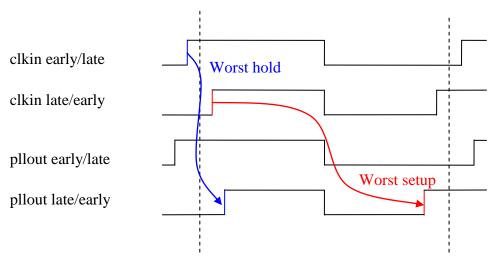

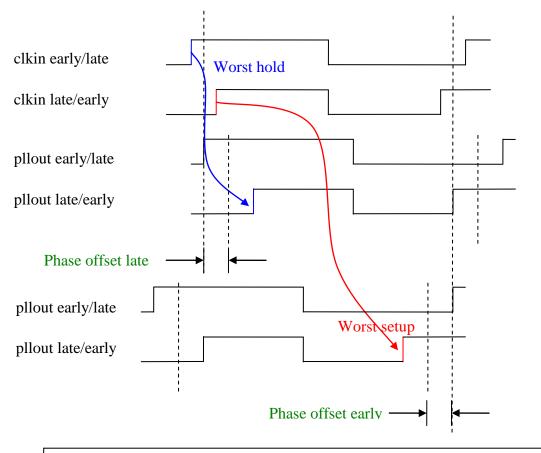

But pll phase error will certainly affect paths between the pll clock and the ref clock, just as if it were pll cycle-to-cycle jitter:

Setup margin reduced by : clkin\_c2cjitter(+) + phase\_offset(-) + pll\_c2cjitter(-) Hold margin reduced by : clkin\_c2cjitter(-) + phase\_offset(+) + pll\_c2cjitter(+)

Figure 4-5

Here is a table summarizing which type of jitter affects which paths:

| Type of       | Same-clock | Same-clock | Refclk       | Refclk     |

|---------------|------------|------------|--------------|------------|

| jitter        | setup      | hold       | to/from      | to/from    |

|               |            |            | pllclk setup | plick hold |

| Pll cycle-to- | Yes        | No         | Yes          | Yes        |

| cycle         |            |            |              |            |

| Refclk        | Yes        | No         | Yes          | Yes        |

| cycle-to      |            |            |              |            |

| cycle         |            |            |              |            |

| Pll phase     | No         | No         | Yes          | Yes        |

| error         |            |            |              |            |

Figure 4-6

Note that I have used a very simplified definition of jitter in these examples. It might be worse than this. If you allow the refclock to have its maximum jitter for N cycles, and the pll clock to have its maximum jitter for M consecutive cycles, then you get setup/hold reductions of: N\*refclk\_max\_jitter + M\*pllclk\_max\_jitter (where "max\_jitter" means the max excursion from nominal – 100ps for a jitter of +/- 100ps). Ultimately this will have to be limited by the "long-term jitter" spec. If we define "long term jitter" as "the absolute maximum difference between the edges of the refclk and the pll clock under any and all circumstances", then perhaps we should replace the "refclk\_c2c\_jitter + pllclk\_c2c\_jitter + phase\_error" with a single term – the long-term jitter. Or, since the long-term jitter spec was probably derived using a jitter-free reference clock, perhaps the correct answer is "refclk\_c2c\_jitter + pll\_long\_term\_jitter".

Of course, we're not free to define any of these terms. What matters is how the PLL designer defines them. Since there is, as far as I can tell, no clear industry-accepted definition of jitter specs, it is important to know what the person who created the spec meant.